Computer Science > EXAM > University of Maryland, College ParkENEE 446. ALL ANSWERS CORRECT-GRADED A. (All)

University of Maryland, College ParkENEE 446. ALL ANSWERS CORRECT-GRADED A.

Document Content and Description Below

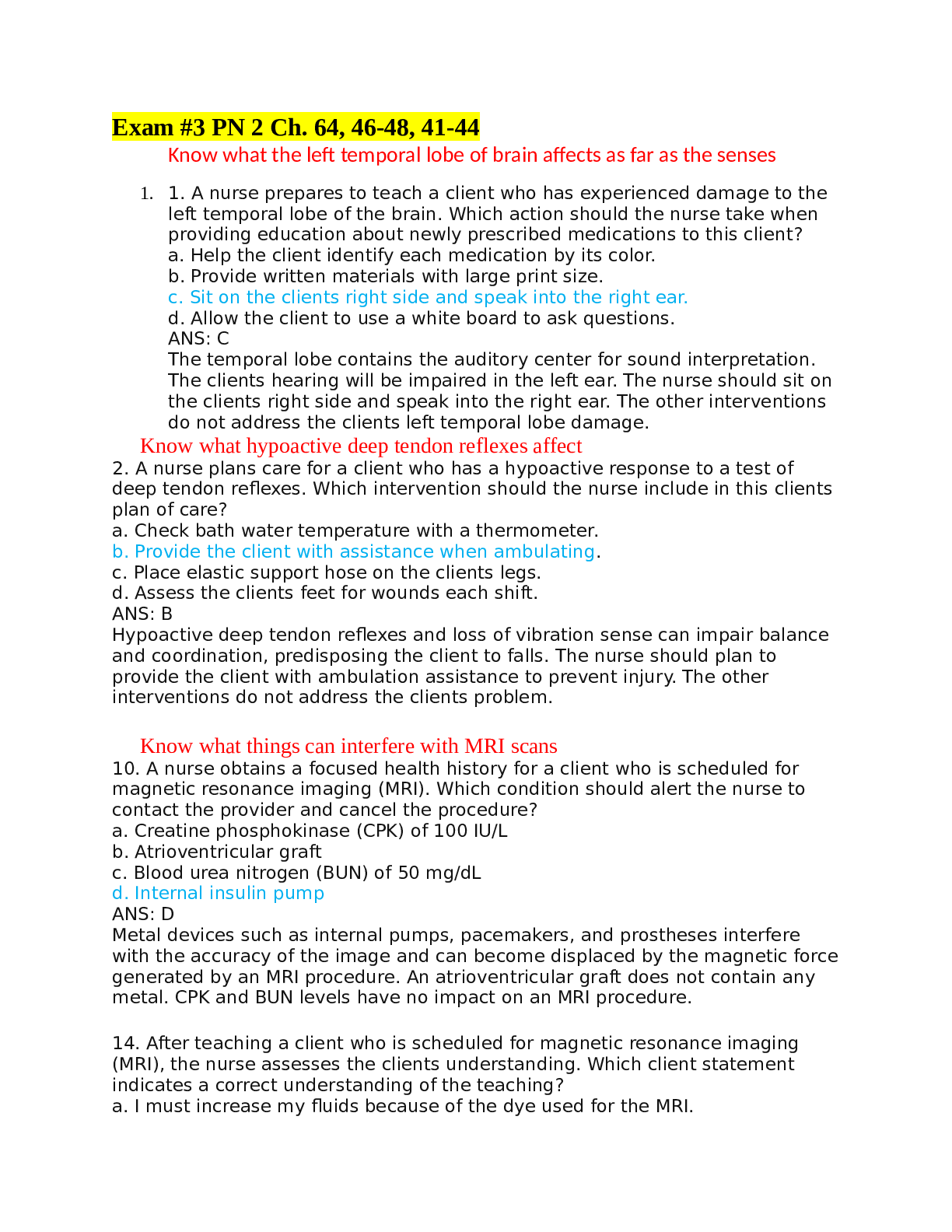

ENEE 446 (Section 201) Fall 2008 Midterm Examination Pages: 6 printed sides Name: __________________________________________ Time alloted: 1 hour 15 min Student ID: ________________________________... ______ Maximum score: 63 points University rules dictate strict penalties for any form of academic dishonesty. Looking sideways will be penalized. Look at only your own exam at all times. There are 6 questions, some with subparts. Read them carefully to avoid throwing away points!! Write your answer in the space provided. Closed book, closed notes. Calculators are allowed. Partial credit rule: Must show your intermediate steps clearly for partial credit! 1. Fill in the blanks with a few words: (1 point * 12 = 12 points) (a) In ____________________________ computers, availability and throughput are more important than the speed of a single task. (b) Moore’s law trends in recent years have resulting in the presence of multiple _________________________ in each processor chip. (c) For hard disks, their ________________________ has been rapidly growing each year. (d) An important result of _________________________ law is that improving the common case results in the most improvement in computer performance. (e) The ________________________________ (a performance metric) of a MIPS pipeline falls to below one in the presence of pipeline stalls. (f) ______________________________ improves the run-time of computers since it exploits the parallelism between sub-tasks in sequentially issued instructions, even when they might be data-dependent. (g) The ________________________ stage in the MIPS pipeline computes the effective address of memory instructions. (h) The instruction cache memory is accessed in the ______________________________stage of the MIPS pipeline. (i) Using a unified cache for the MIPS pipeline would cause a __________________________ hazard for memory instructions. (j) In a 5-stage MIPS pipeline, the data hazard stall between a __________________________________ instruction and a subsequent dependent DADD instruction cannot be removed by bypassing. (k) Suppose the branch condition and target become known in the EX stage, then the branch penalty is ____________________________ cycles. (l) A branch whose subsequent instruction is always executed regardless of the branch outcome is called a __________________________ branch. Answer key server cores (processors okay) capacity (size okay) Amdahl’s IPC Pipelining EX IF structural LW/ LD /load two delayed [Show More]

Last updated: 1 year ago

Preview 1 out of 6 pages

.png)

Reviews( 0 )

Document information

Connected school, study & course

About the document

Uploaded On

May 02, 2021

Number of pages

6

Written in

Additional information

This document has been written for:

Uploaded

May 02, 2021

Downloads

0

Views

52

.png)

.png)

.png)